FIFO (First Input First Output) simply means FIFO. Due to the rapid development of microelectronics technology, the capacity of new generation FIFO chips is getting larger and smaller, and the volume is getting smaller and smaller, and the price is getting cheaper and cheaper. As a new type of large-scale integrated circuit, FIFO chips are increasingly used in high-speed data acquisition, high-speed data processing, high-speed data transmission, and multi-machine processing systems due to their flexible, convenient, and high-efficiency characteristics.

In system design, FIFO memory is widely used for the purpose of increasing data transmission rate, processing a large number of data streams, and matching systems having different transmission rates, thereby improving system performance. The FIFO memory is a first-in, first-out, dual-port buffer in which the first data entered therein is first shifted out, with one memory input port and the other memory output port. For a single-chip FIFO, there are two main structures: trigger-oriented structure and zero-oriented transmission structure. The FIFO of the trigger-oriented transfer structure is composed of a register array, and the FIFO of the zero-oriented transfer structure is composed of a dual-port RAM having read and write address pointers.

FeaturesThe FIFO memory is the buffering part of the system. If there is no FIFO memory, the whole system cannot work normally. It mainly has several functions:

1) Cache continuous data streams to prevent data loss during incoming and storage operations;

2) The data is gathered together into the machine and stored to avoid frequent bus operations and reduce the burden on the CPU.

3) Allow the system to perform DMA operations to increase data transfer speed. This is a crucial point. If you do not use DMA operation, data transmission will not meet the transmission requirements, and it will greatly increase the burden on the CPU and cannot complete the data storage at the same time.

Therefore, choosing the right memory chip is very important for improving the system performance. In past designs, the “Ping-Pong†storage method is often used. This method uses two pieces of memory, and the data first enters one of them. When the data is full, Let the data enter the second piece of memory, and at the same time, the data in the first piece of memory is removed through logic control, and so on. Two pieces of data are buffered in turn. This method has obvious disadvantages. Firstly, the control is complicated and special logic is needed to maintain this rotation mechanism. Secondly, the flow of data flow must be constantly changed, which limits the data flow rate and is also prone to interference. From the data transmission point of view, the greater the capacity of the cache chip, the lower the requirement for subsequent timing, which can reduce the frequency of bus operations; but from the perspective of data storage, it means that there is a need to open up more memory space for buffering. Increase the computer's memory overhead, and the larger the capacity, the higher the cost. Therefore, based on a comprehensive consideration of system performance and cost, a chip that satisfies the system needs can be selected.

FIFO is the abbreviation of First In/First-Out. It means first in, first out. The FIFO memory is divided into a write private area and a read private area. The read operation and the write operation can be performed asynchronously, and the data written on the write area is read from the area of ​​the read terminal in the order of writing, similarly to a kind of buffer absorbing the speed difference between the write end and the read end. The computer's serial port, in general, also has a FIFO buffer (not a single FIFO memory, but embedded inside the device).

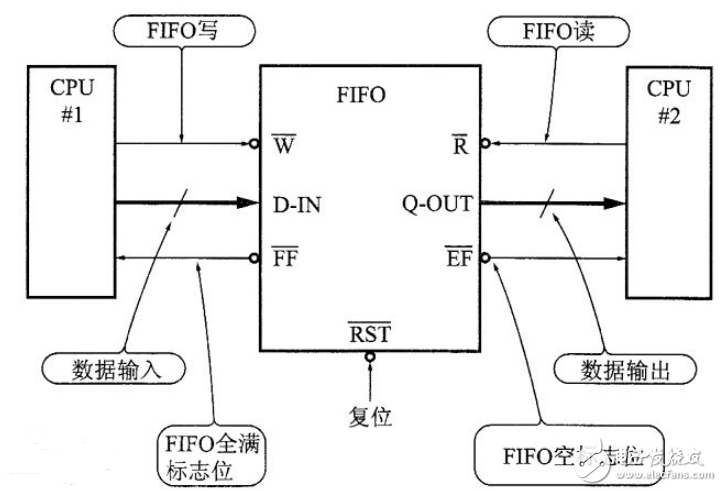

The connection mode of the FIFO memory is as shown in the figure. A status pin indicating an internal buffer status (Buffer Full; Buffer Empty, Buffer Empty) is added to the FIFO memory instead of the address bus, and both sides connected to the FIFO use this status to control the operation. In addition, the reset pin of the FIFO is reinitialized (without data status) upon power-on and reset or due to some abnormality in operation. This can be said to be a characteristic of the FIFO memory.

What are the fifo memory chip models?1) Patch FT245BL Single FIFO Memory USB Interface Controller Chip Bidirectional LQFP32 Package

The IDT72V3680 is one of IDT's high-density supersyncTMII 36-bit series memory IDT72V3640 to 3690 with a storage structure of 16,384×36. This series of CMOS process FIFO (first in, first out) chips have great depth.

3) CY7C4235-15AC FIFO memory IC CY7C4235 TQFP-64 chip

4) United States IDT FIFO memory IC chip 7203L20TDB

5) CY7C4205-10AC FIFO chip IC TQFP64v

6) FDTI new FT2232HL LQFP-64 USB interface to serial port 2 channel transceiver chip 70mA

7) IDT72V04L25J IDT new original PLCC package logic - FIFO memory chip

8) CH424Q QFP44 new lead-free original 4K byte capacity FIFO memory chip

Security Zinc Alloy Die Casting

Security Zinc Alloy Die Casting,Aluminium Pressure Die Casts,Steel Die Casting Aluminum Alloy,Customized Zinc Alloy Die Castings

Dongguan Metalwork Technology Co., LTD. , https://www.dgdiecastpro.com