As processors are added to traditional FPGAs, programmability is added to the ASIC, and the boundaries between FPGAs and ASICs are increasingly blurred.

FPGAs have become more popular than ever. Today's FPGAs are no longer just a simple combination of look-up tables (LUTs) and registers. They have become the architecture for system exploration and a bridge to validate future ASIC design architectures.

From basic programmable logic devices to complex SoC devices, today's FPGA family is extremely large. In a variety of applications, including automotive and other applications such as AI, enterprise networking, aerospace, defense, and industrial automation, FPGAs enable chipmakers to deploy implementation systems in newer ways when needed. The flexibility of FPGAs is critical in such standards, protocols, and best practices that are still being explored and in cost-competitive emerging markets.

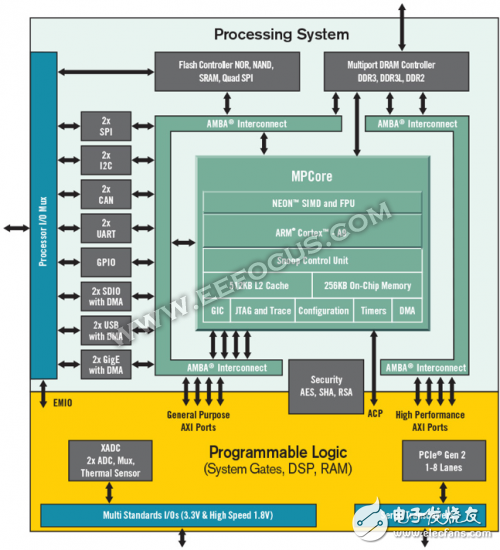

That's why Xilinx decided to add an ARM core to its Zynq FPGA to create an FPGA SoC, said Louce de Luna, marketing director at Aldec. “The most important thing is that the vendor has improved the tool flow, which has generated a lot of interest in Zynq. Their SDSoC development environment looks a lot like the C language and is very friendly to developers because the application is usually Written in C. They put software functionality into the development environment, allowing users to assign these features to specific hardware."

Some of these FPGAs are not just SoCs, they are SoCs themselves.

"They may include multiple embedded processors, dedicated compute engines, complex interfaces, and mass storage," said Muhammad Khan, Integrated Verification Product Specialist, OneSpin SoluTIons. “System architects plan and use the resources available to FPGAs, just as they do on ASICs. Design teams use synthesis tools to map their System Verilog, VHDL, or System C RTL code to the underlying logic elements. For most In the design process, design differences specific to FPGAs or ASICs or full-custom chips are decreasing."

ArterisIP Chief Technology Officer Ty Garibay is very familiar with this evolution. "Xilings began practicing this route on Zynq in 2010. They defined a product that incorporated the ARM SoC hard macro into the existing FPGA at the time," he said. “Then, Altera recruited me to do basically the same thing. Its value proposition is that many customers want the SoC subsystem, but the features of the SoC, especially the processor, are not suitable for integration into the FPGA. The ability to embed functionality into actual programmable logic is prohibitive because it almost exhausts the entire FPGA's resources. But it can be used as a hard part of the entire FPGA chip, as a hard feature. You don't have the ability to provide true reconfigurable logic for SoCs, but they can be programmed in software to change functionality in this way."

“This means that this architecture can have both software programmable features, hard macros and hardware programmable features that they can work together,†he said. “There are some fairly good target markets during this period, especially in the low-cost automotive control field, where a medium-performance microcontroller is typically paired with an FPGA. Now customers will say, 'I can now Features are placed on the hard macro of the FPGA chip to reduce board space, reduce BOM and reduce power consumption.'"

This is also in line with the development trend of FPGAs in the past 30 years. The original FPGA was just a programmable structure and a set of I/O. Over time, the memory controller, SerDes, RAM, DSP, and HBM controllers are slowly hardened.

Garibay said: "FPGA vendors continue to increase chip area, and continue to add more and more hard logic, which is widely used by a large proportion of customers. Now, these hard logics are turned into software programmable devices. Most of the things added before the ARM SoC are different forms of hardware, mainly related to I / O, but also include DSP, DSP has enough application plans, so by hardening the DSP, you can save programmable logic gates. â€

Market possibility

This approach has basically turned the FPGA into a Swiss Army Knife with many possibilities.

"If you look back, FPGAs are just a bunch of LUTs and registers, not gates," said Anush Mohandass, vice president of marketing and business development at NetSpeed ​​Systems. “There is a typical problem here. If you compare any general-purpose device to a dedicated device, you will find that general-purpose computing provides more flexibility, while dedicated computing can provide performance or efficiency advantages. Xilinx and Altera have been trying to The more I combine general-purpose computing with dedicated computing, they notice that almost every FPGA customer has DSP and some form of computing. So they added the ARM core, DSP core, and all the different PHYs to the FPGA. And common modules, they harden these things, making them more efficient and the performance curve getting better."

These new features open the door for FPGAs to play an important role in a variety of emerging and existing markets.

"From a market perspective, you can see that FPGAs will definitely enter the SoC market," said Piyush SancheTI, senior marketing director at Synopsys. “It’s an economic problem to be an FPGA or a mature ASIC. Their boundaries are beginning to become blurred, and we’re seeing more and more companies – especially in certain markets – are in the mass production phase. Use a lower cost FPGA."

Historically, FPGAs have been used primarily in the prototype phase, and in production use, it is limited to markets such as aerospace, defense, and communications infrastructure, SancheTI said. “The market is now expanding into automotive, industrial automation and medical equipment.â€

AI: A thriving FPGA market

Some system vendors/OEMs use FPGAs to optimize their IP or AI/ML algorithm performance.

NetSpeed's Mohandass said: "They want to build their own chips. For many of them, doing ASICs may be a little scary. They may not want to spend $30 million on wafer costs to get chips. For them, FPGAs are An effective entry point, they have unique algorithms, their own neural networks, and they want to engineer and see if it can deliver the performance they expect."

Stuart Clubb, senior product marketing manager for Catapult HLS Synthesis and Verification at Siemens subsidiary Mentor, said the current challenge for AI applications is quantification. "What kind of network do you need? How do I build this network? What kind of memory architecture? Even if you only have a few layers of neural networks, when you get a lot of data with a few coefficients, it will quickly turn into millions of coefficients. Storage bandwidth can also become terrifying. No one really knows what the correct architecture is. If you don't know the answer, you certainly won't design an ASIC directly."

In the corporate network space, the most common problem is that password standards seem to be changing. Mohandass said: "It's better to put the crypto engine in the FPGA instead of trying to build an ASIC." Or, if you do any type of packet processing in a global network, the FPGA still gives you more flexibility and More programmability. This is where flexibility comes in, and they have taken advantage of this flexibility. You can call it heterogeneous computing, it still looks like an SoC. â€

New rule

With the introduction of the new generation of FPGA SoCs, the old rules no longer apply. "Specifically, if you're still debugging on the board, it's too late," Clubb pointed out. “While debugging on the development board is considered a lower cost solution, it is the means used in the early stages: 'It is programmable, you can place an oscilloscope on it and observe the phenomenon. See what happens. If I find an error, I can fix it, modify the code in a day, then re-burn it to the board, and then locate the next bug, 'This is crazy. In the employee's Time is not considered a cost for many companies, management will not buy simulators or system-level tools or debuggers, because 'I paid for this person to complete the work, I will always train him until he works hard.'"

This behavior is still very common, Clubb said, because many companies implement a 10% final elimination to motivate each employee to work.

However, FPGA SoCs are true SoCs that require rigorous design and verification methods. “Device programming doesn't really affect design and verification,†says Clubb. "If you want to design a SoC, you can follow the block diagram method of the 'Lego' project that I have heard from many customers. I need a processor, a memory, a GPU, some other parts, and a DMA memory controllers, WiFi, USB and PCI, these are the 'Lego' blocks you assemble. The trouble is that you have to verify that they work and work together."

However, FPGA SoC system developers are quickly grasping the verification methods that SoC practitioners are concerned about.

"Because the cost of using FPGAs is lower, FPGA SoC system developers think differently than traditional chip SoC developers. The traditional SoC developers are thinking that 'this will cost me $2 million, so I'd better. Be prepared for the best," Clubb said. "But if you spend $2 million to develop an FPGA, don't get it right, now you will need to spend three months fixing these bugs, which is also a cost to consider. How big is the development team? How much does it cost? Not listed in time What are the penalties? These are very difficult to quantify. If you are in the consumer sector, it is almost impossible to use FPGAs on products that are available for sale during the Christmas season, so this has a different priority. Do it in custom chips. An SoC needs to face huge overall costs and risks, so it is becoming less and less common. As we all know, the industry is consolidating and there are fewer and fewer players. Each player must find a way to implement their own designs. The FPGA SoC can help achieve this goal."

New compromise

SancheTI said that many engineering teams don't mind replacing target devices. “We have seen many companies create RTL and validate it, but hardly know if they will choose FPGA or ASIC, because this decision may change many times. You can start with FPGA, when a certain amount is reached, if ASIC costs Lower, go to the ASIC."

This situation is especially prevalent for today's AI applications.

Mike Gianfagna, vice president of marketing at eSilicon, said: "The technology to accelerate the speed of AI algorithms is still evolving. Artificial intelligence algorithms have been around for a long time, but now, we suddenly become more complicated in using AI, and can be very Magically running them at near real-time speed. The original AI algorithm runs on the CPU and then moves to the GPU. The GPU can also be considered a programmable device, although it has some versatility. The GPU architecture excels at parallel processing. Because the graphics acceleration operation is parallel computing, it is convenient to run the AI ​​algorithm on the GPU, because AI is basically parallel processing. To a large extent, the GPU is really good, but it is still a general method, you can A certain degree of performance is achieved with a certain amount of power consumption. Now, some people will turn to the FPGA to run the AI ​​algorithm, because the FPGA can provide better dedicated circuits than the GPU, and the performance and efficiency can be improved. The best in terms of power consumption and performance, because you have a custom architecture that can fully meet your needs, not much Quite a lot, obviously the best."

Artificial intelligence algorithms are difficult to map onto the chip because they are almost always changing. As you can see, it is completely out of date to make a fully customizable ASIC, because the old algorithm is outdated when the chip leaves the factory. "FPGAs are clearly good at dealing with this situation because you can reprogram them so that the expensive investment in the chip won't be lost," Gianfagna said.

Here are some custom memory configurations, as well as some subsystem functions like convolution and transpose storage that can be reused, so although the algorithm may change, some blocks don't change and can be used again and again. . With this in mind, eSilicon is developing a chassis with software analysis capabilities that can detect AI algorithms with the goal of selecting the best architecture for a particular application more quickly.

"With FPGAs, you have the flexibility to change machines or engines because you may encounter a new neural network, and choosing an ASIC takes risks because you may not be able to get the flexibility," said Deepak Sabharwal, vice president of intellectual property engineering at eSilicon. . "However, FPGAs are always limited in terms of capacity and performance, so FPGAs can't really reach product-level specifications. You can use it to experiment and group things, but in the end you will have to choose an ASIC."

Embedded LUT

In the past few years, there has been some advance in a device type, the embedded FPGA, which integrates programmability into the ASIC while adding the performance and power advantages of the ASIC to the FPGA.

Geoff Tate, CEO of Flex Logix, said: "In FPGA SoCs, the processing unit has a relatively small chip area. In the block diagram, the ratio is large or small, but in actual lithography, it is still mainly FPGA. However, there is a class of applications and customers, and the correct ratio of FPGA logic cells and the rest of the SoC should be smaller for the FPGA, making them both RTL programmable and more cost effective.

This approach has received considerable attention in aerospace, wireless base stations, telecommunications, networking, automotive, and visual processing applications, particularly in artificial intelligence applications. "The algorithm changes so fast that the chip is almost out of date when it comes back from the fab," Tate said. “With embedded FPGAs, designers can iterate their algorithms faster.â€

This is especially true in the evolution of cars from driver-driven to autonomous vehicles. Raymond Nijssen, vice president of systems engineering at Achronix, said that while failure and aging issues have caused a lot of attention, the main challenge is to maintain "elegant degradation." “Over time, performance and quality will change and standards will change. For example, a relatively new requirement is that cars need to recognize children crossing the road, no one knows how these regulations will change, or how you test, How to test those standards that are not yet known."

In this case, Nijssen says that programmability is critical to avoid re-creating the entire chip or module.

Debug your design

As with all SoCs, understanding how to debug these systems and how to build measurements can help people identify problems before they have big troubles.

"As system FPGAs become more and more like SoCs, they need a set of SoC-like development and debugging methods," said UltraSoC CEO Rupert Baines. “There is a naive idea that you can see anything in the FPGA, so it's easy to debug. The waveform viewer can look at the bit level, but it doesn't provide any system level information. Now the new large FPGA is obviously the system. At the system level, the waveform-level view you get with the bit detector doesn't make much sense. What you need is a logic analyzer, protocol analyzer, and good debug and trace capabilities for the processor core itself."

The size and complexity of an FPGA requires that the verification process be similar to an ASIC. Advanced UVM-based test platforms support simulation and often support simulation. From automatic design checks to assertion-based verification, and a range of powerful solvers, formal tools play a key role here. Although FPGAs can indeed be modified faster and cheaper than ASICs, the difficulty of detecting and diagnosing bugs in large SoCs means that they must be thoroughly verified before entering the bring-up phase, OneSpin's Khan said.

In fact, the verification requirements for FPGA SoCs may be higher than for ASICs in terms of equivalence checking between RTL inputs and integrated netlists. Compared to traditional ASIC logic synthesis processes, the refinement, synthesis, and optimization phases of FPGAs often require more modifications to the design. These changes may include moving logic across cycle boundaries and implementing registers in the memory structure. Khan adds that a thorough sequential equivalence check is critical to ensure that the final FPGA design is still consistent with the original designer intent in RTL.

There is also room for optimization in terms of tools. "Many embedded visual applications are written on Zynq and the performance may be 5 frames per second. But if you accelerate it on hardware, it could increase to 25 to 30 frames per second, and this room for improvement paves the way for new devices. The problem is that the simulation and verification of these devices is not straightforward. You need to integrate software and hardware, which is difficult. If you put all the operations in the SoC, it's too slow. Each simulation can take five to seven hours, and if you combine multiple simulations, you can save time,†Aldec's de Luna said.

In short, the same methods used in complex ASICs are now being used in complex FPGAs. As these devices are used for functional safety type applications, this becomes increasingly important.

“This is where the formal analysis comes in. Through formal analysis, you can get the wrong path of communication and then verify those paths,†said Adam Sherer, marketing director at Cadence. “These things are great for formal analysis. Traditional FPGA verification methods are almost impossible to perform these types of verification. There is a very popular view that FPGA design is very fast and can easily run hardware tests at system speed, and only A simple simulation can be performed for integrity checking. Programming is programmed into the device and running in the lab. This is a relatively fast verification path, but the observability and controllability in the lab is extremely limited. Because it can only be probed based on the data on the FPGA pins so you can see them on the tester."

Dave Kelf, chief marketing officer of Breker Verification Systems, agrees. "This has made an interesting shift in the way these devices are validated. In the past, on small devices, it was verified by loading the design into the FPGA and running it on the test card as much as possible. As the SoC and With the advent of software-driven design, it is expected that this "self-designed prototype" verification approach may be applicable to software-driven technologies and may be applicable to certain stages of the process. However, identifying and debugging problems on prototypes is complex. This early verification phase requires simulation, so SoC-type FPGAs look more and more like ASICs. The versatility between SoCs and FPGAs makes the verification process more efficient, and debugging and test platforms are common. Portable Stimulus (portable excitation) and other new Progress will provide this versatility and will actually make SoC FPGAs easier to manage."

in conclusion

Looking ahead, Sheerer said that users are looking to apply the more rigorous processes now used in the ASIC space to FPGA processes.

“There are many learning and analysis applications that want more system-level debugging techniques in FPGAs,†he said. “The FPGA community has always been behind the latest technology and tends to use very traditional methods, so they need to train and understand the latest technologies and methods, planning, management and traceability of requirements. FPGAs absolutely need those elements from the SoC process. The driving force comes from the industry standards in end applications, not the FPGA itself. Traditional FPGA engineers need to be re-educated."

The boundaries between ASICs and FPGAs are becoming increasingly blurred in applications that require flexibility, system architectures that continually combine programmable logic and hard-wired logic, and tools that work with both. This trend will not reverse in the short term, as many new application areas that require these combinations are still in their infancy.

4G Outdoor Cpe,4G Lte Outdoor Cpe Router,4G Lte Outdoor Cpe,Outdoor 4G Lte Cpe Router

Shenzhen MovingComm Technology Co., Ltd. , https://www.movingcommiot.com