What factors need to be considered when the ADC clock is input? How can I make the ADC fully utilize the performance of the chip? Let Ian Beavers, Senior Engineer, Digital Video Processing, Analog Devices, tell you!

To get the most out of your chip, you should use a differential signal to drive the sample clock inputs (CLK+ and CLK−) of the ADC. Typically, this signal should be ac-coupled into the CLK+ and CLK− pins using a transformer or capacitor. These two pins have an internal bias and no additional bias is required.

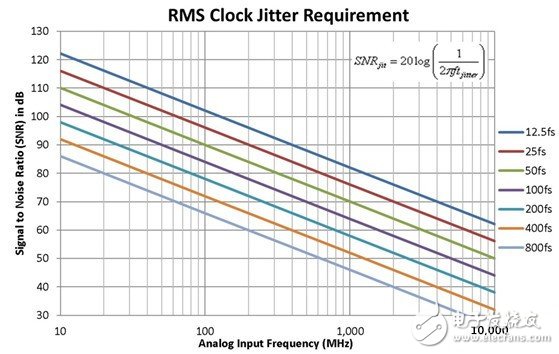

High speed, high resolution ADCs are very sensitive to the quality of the clock input signal. To achieve excellent signal-to-noise ratio (SNR) for high-speed ADCs, root mean square (rms) clock jitter must be carefully considered based on the required input frequency. Rms clock jitter can limit SNR, even for the best performing ADCs, which can be even more severe when the input frequency is high. At a given input frequency (fA), the SNR drop due to aperture jitter (tJ) is calculated as follows:

SNR = 20 &TImes; log10 (2 &TImes; π &TImes; fA &TImes; tJ)

In the equation, the rms aperture jitter represents the root mean square of all sources of jitter, including the clock input signal, the analog input signal, and the ADC aperture jitter. The IF undersampling application is especially sensitive to jitter, as shown in the following figure. When the rms clock jitter is the same, if the ADC's analog input frequency is tripled, the SNR will be reduced by 10dB.

The figure shows the performance of the SNR-limited performance versus input frequency for different rms clock jitter conditions. It may be noted that as the input frequency increases, in order to achieve the same SNR limit as at lower input frequencies, rms clock jitter needs to be reduced. For example, when the rms clock jitter is 200fs, the SNR performance limit of the ADC at 250MHz is 70dB, but the 1GHz input signal should achieve the same performance, and the rms clock jitter must be 50fs or lower.

When aperture jitter can affect the dynamic range of the ADC, the clock input signal should be considered an analog signal. To avoid mixing digital noise into the clock signal, the clock driver supply should be separate from the ADC output driver supply. If the clock signal is from another type of clock source (by gating, frequency division, or other method), the original clock should be retimed at the end.

ZGAR Aurora 500 Puffs

ZGAR electronic cigarette uses high-tech R&D, food grade disposable pod device and high-quality raw material. All package designs are Original IP. Our designer team is from Hong Kong. We have very high requirements for product quality, flavors taste and packaging design. The E-liquid is imported, materials are food grade, and assembly plant is medical-grade dust-free workshops.

Our products include disposable e-cigarettes, rechargeable e-cigarettes, rechargreable disposable vape pen, and various of flavors of cigarette cartridges. From 600puffs to 5000puffs, ZGAR bar Disposable offer high-tech R&D, E-cigarette improves battery capacity, We offer various of flavors and support customization. And printing designs can be customized. We have our own professional team and competitive quotations for any OEM or ODM works.

We supply OEM rechargeable disposable vape pen,OEM disposable electronic cigarette,ODM disposable vape pen,ODM disposable electronic cigarette,OEM/ODM vape pen e-cigarette,OEM/ODM atomizer device.

Aurora 500 Puffs,Pod System Vape,Pos Systems Touch Screen,Empty Disposable Vape Pod System,500Puffs Pod Vape System

ZGAR INTERNATIONAL(HK)CO., LIMITED , https://www.szdisposable-vape.com